### POWER OPERATIONAL AMPLIFIER DESIGN IDEAS

## **PA78 DESIGN IDEAS**

HTTP://WWW.APEXMICROTECH.COM (800) 546-APEX (800) 546-2739

#### I. INTRODUCTION

The rapidly expanding interest in piezoelectric actuators has made demands upon operational power amplifiers for higher speed and low power dissipation. These devices can produce motions in sub-nanometer increments and are extraordinarily fast, responding to any change in the applied voltage in just microseconds.

To meet the requirements of piezoelectric designs, as well as other circuitry requiring high-power, fast slew-rate drivers, Apex Microtechnology developed the PA78 power operational amplifier. This IC employs a unique patented circuit and a first for a commercially-available power operational amplifier.

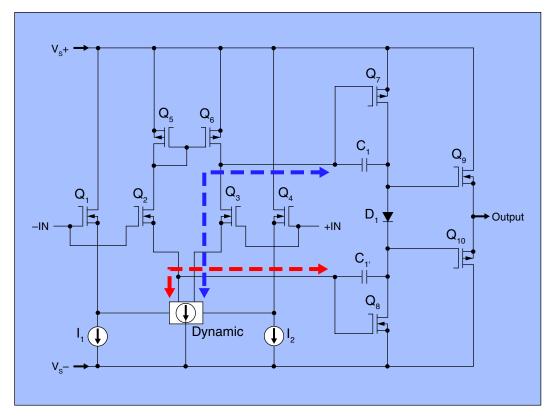

In a traditional power operational amplifier there are several fixed current sources, such as I<sub>1</sub> and I<sub>2</sub>, shown in Figure 1. Because the sources are fixed, they limit the slew rate and dissipate a good deal of power. What makes the PA78 unique is that in addition to its fixed current sources, it employs the dynamic current sources depicted in Figure 1. Consequently, in addition to its normal role of driving the output, the waveform applied at the input of the PA78 also causes the dynamic current sources to supply the necessary current to sink and

source the device capacitances. This enables the output MOSFETs  $Q_9$  and  $Q_{10}$  to achieve slew rates as high as 350 volts per microsecond. What's more, whenever the PA78 is idle, its quiescent current is very low – less than 2.5 milliampere — so even when powered by 350 volts, the quiescent power is less than a watt. This is far less than traditional power operational amplifiers in a comparable circuit. What follows are three circuits that have been developed to fulfill various roles in piezoelectric designs.

**Figure 1.** Dynamic Current Sources Dramatically Enhance Performance — Providing the instantaneous currents necessary to achieve high slew rates, yet current consumption at one milliampere when idle, is extremely low.

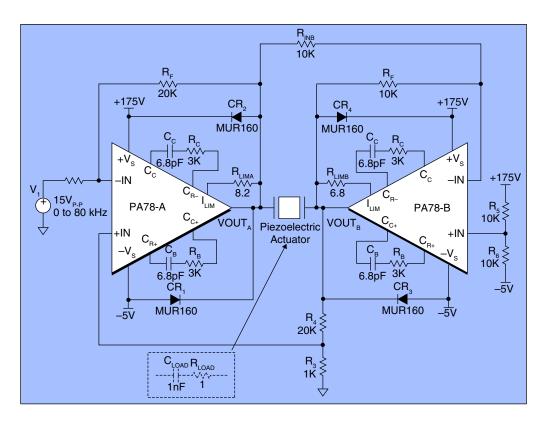

Figure 2. Bridge Connected – A pair of PA78s drive the piezoelectric actuator and are powered by asymmetric power supplies at +175V and -5V.

# II. BRIDGE-CONNECTED PIEZOELECTRIC ACTUATOR DRIVER

A piezoelectric actuator requires a high-voltage driver capable of delivering hundred of volts, peak-to-peak. Since a typical actuator looks like virtually a pure capacitance to the driving amplifier, almost all the power dissipation becomes the burden of the driving amplifier. The circuit configuration shown in Figure 2 fulfills these requirements. The source voltage V $_{\rm 1}$  delivers 15V $_{\rm P,P}$  at a frequency between zero to 80 kHz. The circuit drives the actuator which is represented by the 1-nanofarad capacitance in series with a 1 ohm resistance, as depicted in Figure 2.

Figure 2 also illustrates how two PA78 power operational amplifiers can be connected in a bridge circuit<sup>1</sup>. When configured in this way, these ICs are able to deliver an output voltage swing that is twice that of a single device. This configuration also doubles the single-device slew rate. Another benefit is that any nonlinearities become symmetrical, thereby reducing second-harmonic distortion when compared with a single amplifier circuit.

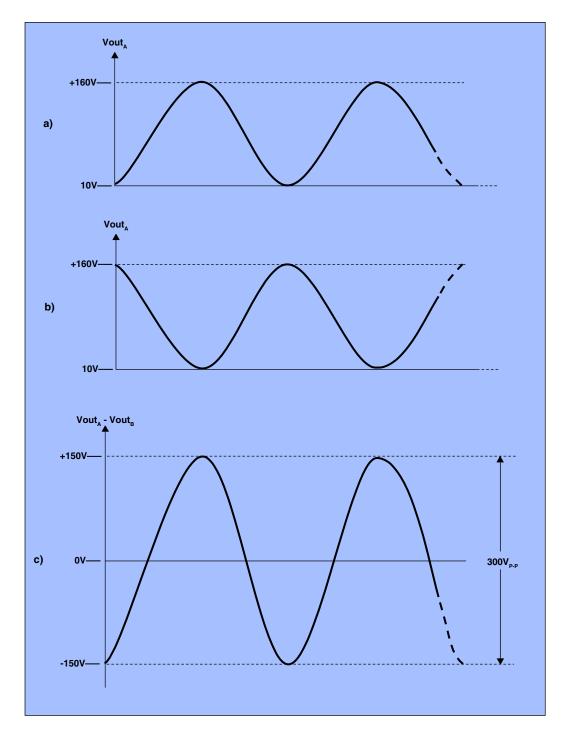

$ilde{\mathbf{A}}$  Floating Load — To say the load is floating means it is not ground-connected. When the left output VOUT $_{\mathrm{A}}$ swings from 10 to 160V (Figure 3a) and the right output VOUT $_{\mathrm{B}}$ descends from 160V to 10V (Figure 3b), a voltage swing of 300V (-150V to +150V) develops across the load, as depicted in Figure 3c.

The outputs of the two amplifiers are now out of phase. The overall gain of the two bridge-configured PA78s is  $\pm 20$ , so that  $300V_{p,p}$  is delivered to the piezoelectric actuator, as required.

As shown in Figure 2, a dual-source, asymmetric power supply delivers +175V and -5V to the two amplifier modules<sup>2</sup>.

**Establishing** +V<sub>s</sub> and -V<sub>s</sub> headroom — The values of +V<sub>s</sub> and -V<sub>s</sub> have been chosen so that there will be sufficient headroom during the positive and negative excursions of both VOUT<sub>A</sub> and VOUT<sub>B</sub> . Though the output (VOUT<sub>A</sub> – VOUT<sub>B</sub>) shown in Figure 3c will swing from +150V to -150V, it is actually the Common Mode Input Range (CMR) positive and negative values of the amplifier and specified in the PA78 data sheet that will play a significant role in governing the values of +V<sub>s</sub> and -V<sub>s</sub> employed in this asymmetrical sourcing arrangement.

In the case of the PA78, the specified value of the CMR negative is  $-V_s + 3V$ . This means the input should approach the negative rail no closer than 3V. By choosing  $-V_s$  equal to -5V, both  $VOUT_A$  and  $VOUT_B$ , having negative excursions to 10V, will approach the negative rail no closer than 15V.

For CMR positive, the value is  $+V_s$  - 2V. This means the most positive-going excursion of both VOUT<sub>A</sub> and VOUT<sub>B</sub> must stay at least 2V below  $+V_s$ .

A second issue with regard to the  $+V_{\rm S}$  rail is the voltage drop at the output when the modules are delivering peak current. In this application the peak current is approximately 75 mA. There is a graph in the PA78 data sheet called "Output Voltage Swing" which denotes that if you are driving this much current you are going to lose approximately 8 volts. The sum of the two, 2V and 8V, is 10V which says the  $+V_{\rm S}$  must be at least 10V above the maximum voltage swing of 150V. By choosing a  $+V_{\rm S}$  of 175V, a headroom margin of 15V will be established.

Figure 3. Output Waveforms – a) Left module output; b) Right module output; C) Waveform appearing across the piezoelectric actuator.

What follows is a discussion of the principal passive components:

$\rm R_{\rm 3}$  and  $\rm R_{\rm 4}$  — The feedback circuit comprising resistors  $\rm R_{\rm 3}$  and  $\rm R_{\rm 4}$  center the outputs of the PA78 ICs about 85V.

$\mathrm{CR_1}$  through  $\mathrm{CR_4}$  — In any piezoelectric actuator circuit it is essential to prevent signals from inadvertently feeding back to the amplifier. A piezoelectric transducer can convert mechanical

energy into electrical energy just as easily as vice-versa. So if something were to bump the transducer, it could create a lot of energy that would travel backwards into the output of the amplifier, which could be destructive. However, by connecting several ultra-fast, MUR160 diodes ( $CR_1 - CR_4$ ) from the output of each amplifier to its corresponding power supply rails, as shown in Figure 2, each amplifier is protected.

Computing the maximum dissipated power per module — The load impedance of the piezoelectric actuator is given by the expression:

R+

$$\frac{1}{j\omega C}$$

= 1+  $\frac{1}{j2\pi(80x10^3)(1x10^{-9})}$  (1)

= 1- j1989  $\approx$  - j1989 Ohms

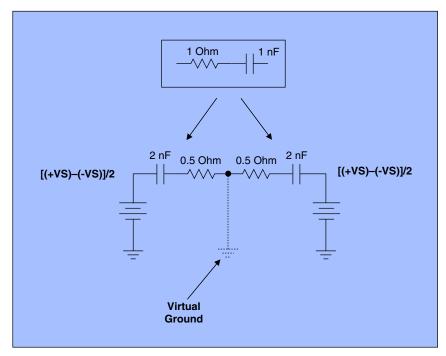

To compute the maximum power per module the equivalent circuit shown in Figure 4 is employed. By doing this, the equivalent circuit of the piezoelectric actuator, shown in Figure 2, is split into two parts with each part comprising a 2nF capacitor and a 0.5 ohm resistor, while assuming a virtual ground denoted by the dotted line and the ground symbol. Since the real part of the impedance (1 Ohm) is negligible compared with the total capacitive reactance of 1989 Ohms, it can be neglected.

In the equivalent circuit depicted in Figure 4, the applied voltage will be one half the total potential applied to each module:

$$0.5[(+V_s) - (-V_s)] = 0.5[(175V) - (-5V)] = 90V$$

(2)

The circuit for each half will drive half the capacitive reactance which is 1989 divided by 2 each — or 994.5 ohms.

The key to determining power dissipation begins with knowing the phase difference between V & I in the load. In this case it is quite simple because we have modeled our load as a pure capacitor, so the phase angle  $\Phi$  is 90 degrees. The formula for determining the maximum power dissipated in the case of a reactive load for a phase angle greater than  $40^{\circ}$  can be found in reference 3.

Figure 4. Equivalent Circuit - For computing the maximum power dissipation for the two PA78s in the bridge circuit.

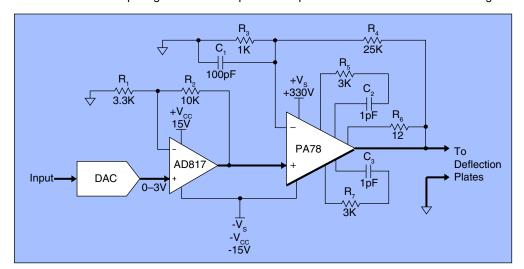

**Figure 5.** Deflection Plates Amplifier Circuit – The fast operational amplifier, AD817, in cascade with the PA78, provide a gain of approximately 100 so that the output voltage applied to the deflection plates can be programmed between 0 and 300 volts.

### III. DRIVING DEFLECTION PLATES

The circuit shown in Figure 5 was developed for 'Continuous Drop' printing applications. In this circuit the PA78 power operational amplifier connects directly to the deflection plates.

Electrostatically-charged ink droplets, typically 50 to 60 microns in diameter, are emitted by the ink source at a high velocity and are then passed through the electrostatically-charged region between a pair of deflection plates. Each droplet is thereby deflected, as required to form the ink characters deposited on the printed surface.

The programming information arrives as a digital data stream at the DAC (digital-to-analog converter) and is converted into a sequence of square waves of differing voltages ranging from zero to 3V. This wave train sequence is then fed to a fast operational amplifier, such as the Analog Devices AD817 shown in Figure 5. The output of this device, in turn, drives the Apex PA78 power operational amplifier.

The output of the PA78 is applied to the deflection plates, as a sequence of square waves, differing in magnitude and varying between zero and 300V at a repetition rate of 100 kHz. At the beginning of each programmed voltage value, the square wave must reach its programmed voltage within 1.5 microseconds. This is essential because the programmed voltage must remain constant throughout the final 8.5 milliseconds, for that is the time span for the next droplet to pass through the deflection-plate field.

Because of its ability to achieve extraordinary high slew rates, as detailed earlier, the PA78 is able to fulfill the objectives of the design. By driving the PA78 hard, the full bandwidth of the PA78 is realized. That is, it can be driven at a pulse repetition rate of 100,000 — or 100 kHz — swinging between zero and 300V, within the rise-time required.

As depicted in Figure 5, the AN817 is programmed to provide a voltage gain of approximately 4V. The Apex PA78 power operational amplifier is programmed to exhibit a gain of approximately 25. Therefore the overall gain from DAC output to PA78 output, is approximately 100V.

Setting  $-V_s$  (- $V_{cc}$ ) to -15V enables both the input and the output of the PA78 to swing all the way to ground.

What follows is a discussion of the principal passive components:

- ${

m C_1}$  The role of this 100pF capacitor is to effectively short-circuit resistor  ${

m R_3}$  during the rise and fall of the square wave so that the gain of the PA78 approaches a very high value, thereby assuring a very fast slew rate.

- $\rm C_2$  and  $\rm C_3$  These are 1pF compensation capacitors employed to assure stability and are discussed in more detail in the PA78 data sheet. In general the smaller they are, the faster the output can swing.

- $\rm R_{_3}$  and  $\rm R_{_4}$  To make sure that the PA78 can operate effectively at 100 kHz, it is essential that the parallel combination of  $\rm R_{_3}$  and  $\rm R_{_4}$  be less than 1 kilohm. The values of  $\rm R_{_3}$  and  $\rm R_{_4}$ , 1 kilohm and 25 kilohms, respectively, meet this criterion while realizing the programmed gain of approximately 25 that is necessary to drive the PA78.

- $\rm R_{\rm 6}$  This current limiting resistor, with a value of 12 ohms, confines the output current to a maximum of 60mA. Though the deflection plates draw no current, the 60mA capability can accommodate any distributed capacitance in the wiring connecting the circuit with the deflection plates. See the PA78 data sheet for further discussion.

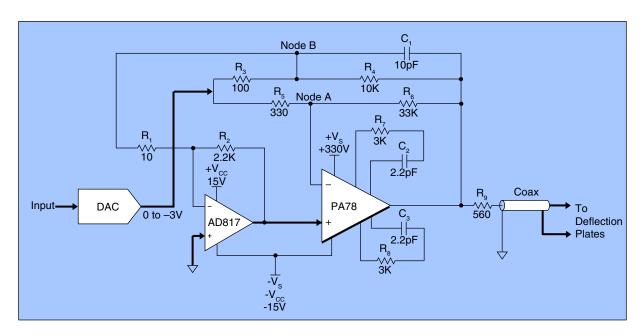

**Figure 6.** Enhanced Slew Rate Circuit – By driving the AD817 from the false summing node (Node B), a slew rate of 350 volts/µs is sustained to within 1 volt of the targeted programming voltage.

### IV. DEFLECTION PLATES DRIVER WITH OVERDRIVE

What is different about the circuit shown in Figure 6, compared with Figure 5, is that it is assumed that the deflection plates are driven via a 25-foot length of coax that exhibits a capacitance of 19.5 pf per foot — or 487.5 pf. Because of this capacitive loading it is a bit more difficult to achieve a satisfactory rise time.

Again a DAC delivers a voltage, this time from zero to -3V to develop an output of 0 to +300V that reaches 299V — or within 1V of the targeted voltage value — within 1.5 microseconds. Again a PA78 power operational amplifier is employed with its ability to source and sink (push and pull) pull current from the differential input stage through the compensation capacitors and the gate-to-source capacitances of the drive stage of the amplifier. As long as the voltage differential across the PA78 + and - inputs is 10V or more, the specified slew rate of greater than 350V per microsecond is maintained.

In general, the design topology depicted in Figure 5, will exhibit this slew rate with little or no overshoot as the amplifier reaches its target voltage. However, as the output of the PA78 approaches its programmed voltage, the (-) input of the PA78 also approaches the non-inverting input (+), thereby reducing the differential voltage and therefore the slew rate.

To meet the 300V swing, as well as the settling requirement of this application, any reduction in the slew rate as the output voltage approaches its target value is unacceptable. However, if a high-speed, small-signal, amplifier is utilized to overdrive the input, the interval of high slew rate can be extended, thereby maintaining a high differential voltage. In this scenario a high slew rate is extended until the amplifier is within 1 volt of the target value (300V).

To achieve this, an AD817 is employed to invert and amplify the potential at the false summing node (Node B), as depicted in Figure 6. The selection of this amplifier need not be limited to the AD817, but a high gain-bandwidth product is critical as well as a slew rate of 300V/µs or more.

A pair of resistors of the same ratio as  $\rm R_5$  and  $\rm R_6$  of the PA78 creates a replica of the real summing node (Node A), at the 'False Summing Node' (Node B). The latter can be monitored without injecting currents into the real summing node at Node A, as this would cause significant static and dynamic errors. This offset voltage is amplified by the AD817 and added as an offset voltage to the (+) input terminal of the PA78. Thus the amplified value of the potential at Node B supplies the overdrive necessary to extend the region of high slew rate to within 1V of the target value

What follows is a discussion of the passive components:

$\rm R_3$  and  $\rm R_4$  — These are the false summing node input and feedback resistors. To perform effectively, the AD817 requires that the summing node impedances be as low as possible. The false summing node resistors in parallel,  $\rm R_3$  and  $\rm R_4$ , are in series with the 10-ohm resistor  $\rm R_1$ , and the equivalent resistor, in turn is connected to the  $\rm R_2$  feedback resistor to form the summing node impedance. The resistance value of the false summing node  $\rm R_3$ -R $_4$ (100-ohm, 10-kilohm) combination makes sure that the AD817 summing node impedance is low.

$\rm R_{\rm s}$  and  $\rm R_{\rm e}$  — These are the real summing node input and feedback resistors. The value of the feedback resistor  $\rm R_{\rm e}$ , 33 kilohms, is a compromise between power dissipation and parasitic capacitance.

To reduce power dissipation you could chose the largest resistance possible because the power consumption goes as the inverse of the resistance and thereby is reduced with a larger resistance. However, the distributed capacitance of a resistor rises as its resistance rises. This tends to slow the slew rate. By connecting several resistors in series to form  $R_{\rm e}$ , and thus connecting the distributed capacitances in series, the resulting value is less than the distributed capacitance of either resistor alone.

This series combination of several resistors is able to reduce power dissipation without adversely affecting the feedback capacitance.

$\rm R_{\rm 9}$  — The isolation resistor  $\rm R_{\rm 9}$  eliminates instability due to the capacitive load. There is a small amount of power dissipated as the capacitor charges, but the final voltage plateau is unaffected.

$\mathrm{C_1}$  — Without the false summing feedback capacitor  $\mathrm{C_1}$ , the overdrive circuit could cause overshoot and excessive settling times. However, by connecting the capacitor in parallel with  $\mathrm{R_4}$ , the overshoot is dampened, without creating stability problems or reducing the slew rate which would be the case if a true feedback capacitor of a much higher value were connected in parallel with  $\mathrm{R_4}$ .

The overall gain of the circuit is governed by both summing node pairs and the gain of the AD817. Simulation has confirmed that by employing 1% resistors, together with the worst case tolerance of the active components, the closed-loop gain error is held to no more than 4%.

### **REFERENCES**

- Apex Microtechnology Corp, Application Note 20 Bridge Mode Operation of Power Operational Amplifiers, www.apexmicrotech.com

- 2. Apex Microtechnology Corp, Application Note 21, Section 3.1 Single Supply Operation of Power Operational Amplifiers, www.apexmicrotech.com

- 3. Apex Microtechnology Corp, Application Note 1, Section 7.2 *General Operating Considerations*, www.apexmicrotech.com **BIBLIOGRAPHY**

"Drive Piezoelectric Actuators With Fast, High-Power Op Amps", by Sam Robinson, Electronic Design Magazine, November 7th, 2005